x86 处理器微架构发展进入全新里程,基于全新 32nm 制程的 Intel Westmere 处理器家族,代号为「 Clarkdale 」的入门至主流级双核心产品,将进一步集成 3D 绘图核心,曾经佔整体 PC 市场 7 成份额的 IGP 晶片组将会成为历史。虽然 Intel 32nm 制程 Westmere 处理器要到明年第一季才会上市,但 HKEPC 又怎会让读者们失望,因此抢先找来全港首颗 Intel Core i3 处理器及 H55 主机板工程样本,与上代 Intel IGP 平台作对比测试。

内建 3D 绘图核心 全新 32nm Clarkdale 双核心处理器

具备改良微架构及全新制程,代号为「 Westmere 」的 32nm 处理器将于 2009 年第四季末量产,基本上,其微架构设计沿自「 Nehalem 」处理器,仅加入了 7 条全新的指令,因此在相同时脉下, 45nm Nehalem 处理器与 32nm Westmere 处理器并没有明显的效能提升,但别忘记「 Westmere 」处理器是「 Tick-Tock 」硅与微架构发展战略的「 Tick 」,其重点并不在于微架构改良上,而是全新制程所带来的生产效益。

「 Westmere 」处理器採用第二代 high-k 配搭金属闸极电晶体,代号为 P1268 的 32 nm 制程,採用 193 浸没式微影技术 (immersion lithography) 于重要的金属层,并配搭 193 奈米或 248 奈米乾式微影技术 (dry lithography) 于非重要的金属层,处理器採用 9 层 Copper layers 及 low-k 内部连结层 (interconnect layers) ,并採用无铅和无卤素封装,而晶片尺寸约为 45nm 产品 的 70% 。

据 Intel 总裁暨执行长 Paul Otellini 指出,全新 32nm 不仅有效降低所需功耗,同时亦能提升核心时脉,强化运算效能,而且亦缩小处理器核心面积,令处理器能内建更多的运算核心或内建绘图核心、 PCI-E 接口及记忆体控制器,晶片组简化为单晶片,可进一步缩小 PC 体积,可切换绘图支援功能,能在内建绘图核心及独立绘图卡之间作出实时切换,达至节能省电效果。

根据 Intel 处理器最新规划, 32nm 「 Westmere 」处理器将于 2009 年第四季正式量产,核心代号为 Clarkdale 的 32 nm 入门至主流级双核心 DT 处理器,将内建 3D 绘图核心,并于 2010 年第一季初出货,紧接着 2010 年第二季中推出代号为 Gulftown 的 32nm 高阶六核心 DT 处理器, 2010 年第四季再推出全新微架构的 32 nm 处理器,代号为「 Sandy Bridge 」,延续「 Tick-Tock 」硅与微架构发展战略。

上星期 HKEPC 编辑部找来全港首颗 Gulftown 六核心处理器,并介绍了 Intel 32nm Westmere 处理器的微架构主要改良,本篇文章则着重于全新「 Clarkdale 」双核心的绘图架构设计,读者想了解更多 32nm Westmere 微架构改良部份,可参考 <<32nm Westmere 六核心 全港首试 Intel 「 Gulftown 」处理器>> 一文。

模组化设计 加快研发时程

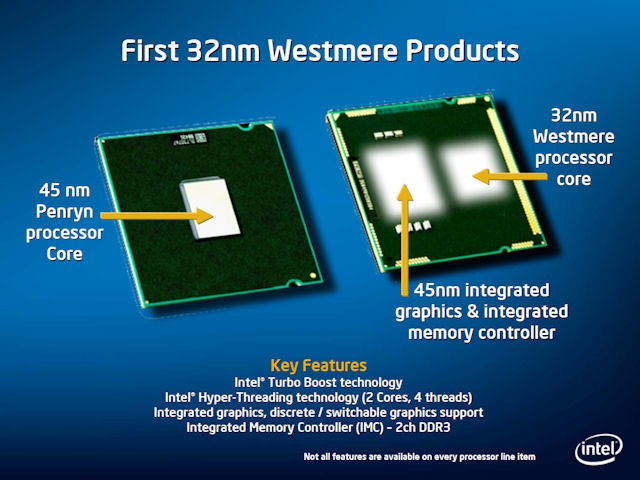

虽然「 Intel Clarkdale 处理器内建绘图核心」这句话并无不妥, 但事实上,其绘图核心并非内嵌于 x86 运算核心之中,而是 x86 核心与绘图核心採用 Multi-Chip Package 封装在一起,其中仅有 x86 核心採用 32nm 制程,绘图核心则採用 45nm 制程。

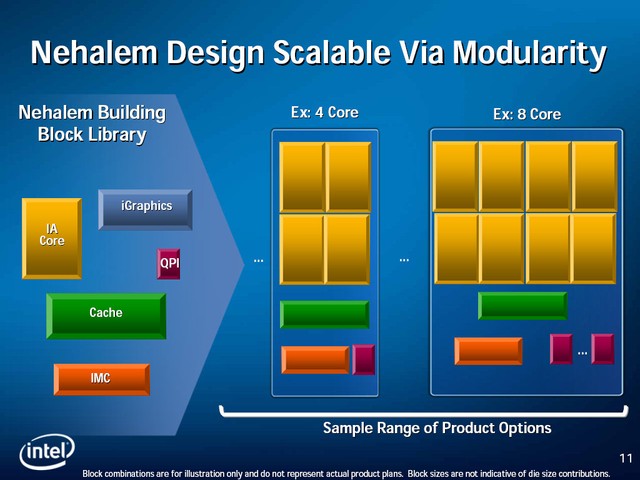

在设计 Nehalem 微架构时, Intel 已加入具扩充性 Building Block 模组化设计,可以轻鬆地提供专门针对各个伺服器、桌面电脑 和行动电脑市场进行优化的架构版本,如此一来, Intel 便可在不需作出改动下,推出涵盖各种价位、性能和效能表现的处理器产品,透过改动处理器核心、 Cache 记忆体、内建绘图核心、系统记忆体控制及 Quick Path Interconnect 的规格组合,以迎合不同市场需求。

Westmere 处理器基于 Nehalem 微架构作出改良,因此同样具备 Building Block 模组化设计, Intel Clarkdale 处理器的 x86 运算核心共有两组处理器核心, 4MB L3 Cache 记忆体,但却抽走记忆体控制器及 PCI-E 控制器,并利用 QPI 通讯协定连接绘图核心。

绘图核心内建记忆体控制器及 PCI-E 控制器,其实说穿了,就是 Clarkdale 处理器纯地把 IGP 北桥晶片直接封装在处理器内。

然而,为何 Clarkdale 处理器不将绘图核心直接内嵌于 x86 运算核心之中?据 Intel 总裁暨执行长 Paul Otellini 先前公开表示,负责处理核心与绘图核心的团队是分开研发,此作法不仅能加快上市时程,且令「 Tick-Tock 」硅与微架构发展战略更具弹性。

Paul 也进一步举例说明,原定 2010 年第一季初推出的是 45nm 制程 Havendale 处理器, x86 处理核心与绘图核心均为 45nm 制程,但由于 32nm 制程 Westmere 核心比预期提早成熟,因此 Intel 把 45nm 制程的 Havendale 取消,直接更新处理核心至 32nm Westmere ,但却保留 45nm 制程的绘图核心,令 Clarkdale 能提前上市。

未来,处理核心与绘图核心的研发团队仍会分开研发,当全新绘图核心完成研发, Intel 可推出新的绘图晶片取代旧有晶片,并配合现有的 x86 处理器一同封装,立即应市,令 Intel 的产品技术升级更具弹性,发挥 Building Block 模组化设计的优势。

Intel 数位企业事业群营运副总裁暨总监 Steve Smith 手持 Clarkdale 实物